General

Conversion Manager

EDWinXP Conversion Manager is used for converting the libraries, databases of EDWin 16-bit compatible to EDWinXP i.e. the 16 bit databases and libraries of EDWin get converted into project database and Libraries compatible for EDWinXP. As the extensions are changed, the extensions of databases and libraries of EDWinXP also are updated. Also EED III Conversion may be done using this utility. This routine converts EE Designer III (ver 2.4 or later) to EDWinXP database format. Conversion may be executed by importing EE Designer ASCII databases. EDWinXP - Export EED3 ASCII Database is a utility that converts schematic diagram and/ or PCB layout design of EDWinXP project to ASCII files in a format acceptable to EE Designer.

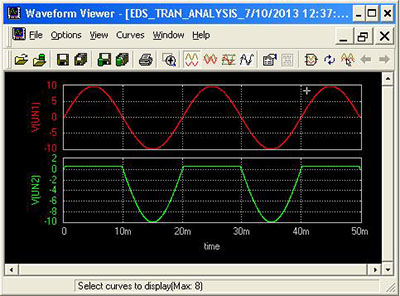

Waveform Viewer

Waveform Viewer may be used to generate results in the form of diagram for Mixed Mode Simulator, EDSpice Simulator and Signal Integrity Simulation. This diagram represents the data generated by simulators to present the simulation results in a graphical format. The graphical format may be displayed on the screen, output to a printer or save it as a part to place it on your actual schematic drawing. The functionality of Diagram Generator has been enhanced to help end users to examine the output diagrams of different analysis in a better way.

In the new Waveform Viewer (the enhanced version of Diagram Generator), there is no limit to the number of variables that may be loaded. At the same time it is capable of handling any number of samples and hence the simulation time has no limit.The diagrams may be saved to or loaded from a project. Several diagrams can be tiled together to view on a single screen. Tools have been made available to allow users to change the presentation style of the diagram with ease.

VHDL Editor

Some main features of EDWinXP VHDL Editor are :

- It compiles the source file and generates wirelist (*.wrs) output file.

- The output file (*.wrs) may be imported directly into EDWinXP.

- Generates simulatable models in Mixed Mode & EDSpice Model Generators .

- Converts the (*.wrs) file to Xilinx,CUPL and JEDEC formats.

VHDL Editor working is very uch similar to any normal programming editor. On compiling the error messages will displayed at the output window below. On double clicking the error the corresponding line in the editor window will get highlighted in Red. This helps in faster debugging of source file. Compilation stops at first occurrence of error and output get displayed in output window. Successful compilation of the .vhdl file generates the .wrs file.

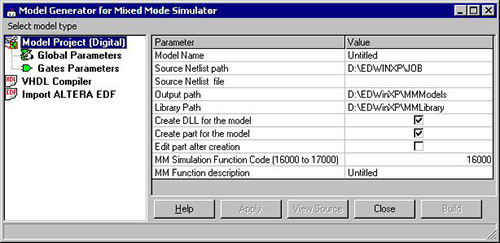

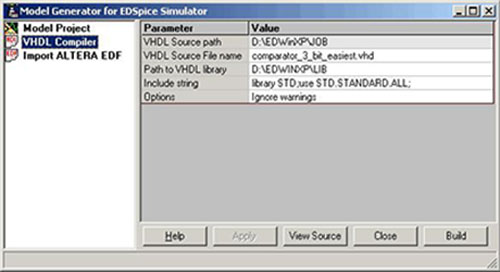

EDWinXP - Model Generators

Model generators allow converting VHDL source files to models for simulation purposes. Since EDWin XP supports two forms of simulation – Mixed Mode and EDSpice, two model generators have been included – MM Simulation Model Generator and EDSpice Simulation Model Generator.

Model Generator for Mixed Mode Simulator - tool converts a vhdl source file to a simulatable component in EDWin XP. This also serves the purpose of making simulation much faster. Since VHDL can be used to create digital models, digital simulation primitives can be created using MM Simulation Model Generator. Earlier, the only way of creating simulation primitives was to model the behaviour of the particular component using Visual C++. Knowledge of programming is naturally not expected of electronic engineers and the need for developing a tool arose which could make creation of models easier.

Model Generator for EDSpice Simulator - tool converts a vhdl source file to a simulatable component in EDSpice, the SPICE based simulator of EDWinXP. This also serves the purpose of making simulation much faster. Since VHDL can only be used to create digital models, only digital simulation models can be created using EDSpice Simulation Model Generator.

Note: EDComX and EDPrimX are tools which can be used for creating both analog and digital models, however it assumes programming knowledge and the user has to build his own simulation primitive dll.

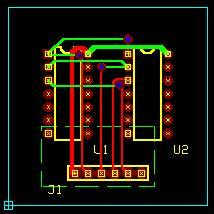

Arizona Autorouter

Arizona autorouter is an integrated module of EDWinXP. It uses its own temporary project and simplified graphics. The Arizona autorouter allows to route the traces of a PCB Layout automatically. The netlists is given as the input to the autorouter. When this router option is selected, all nonorthogonal traces will be removed and accepts only orthogonal traces as pre-routed traces.

SPECCTRA Translator supports different options like converting EDWinXP project (database) to SPECCTRA compatible format, importing results from SPECCTRA Autorouter and Autoplacer etc. MaxRoute Translator allows to convert EDWinXP layout project (database) to a form that is acceptable to MaxRoute Autorouter and MaxRoute Autoplacer.

Subcircuit Adapter allows existing SPICE subcircuits to be converted into an EDSpice format.

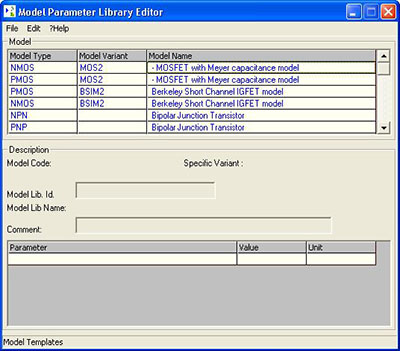

Model Parameter Editor eases the management and creation of model libraries.

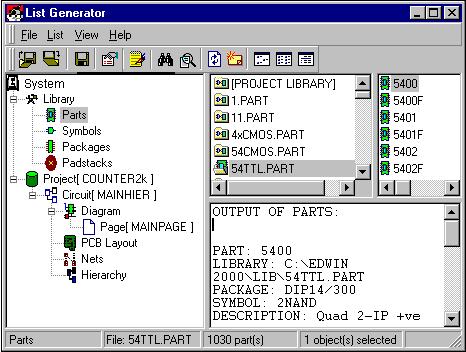

List Generator is a utility that allows generating a list containing requisite details of EDWinXP component library and Project.

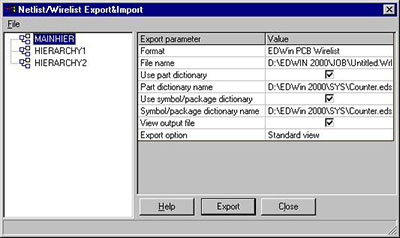

Netlist Import & Export facilitates to transfer information of all the nets or connections involved in the circuit. The information can be transferred to/from third party softwares supporting formats like JEDEC, CUPL, XILINX, ALTERA, etc.

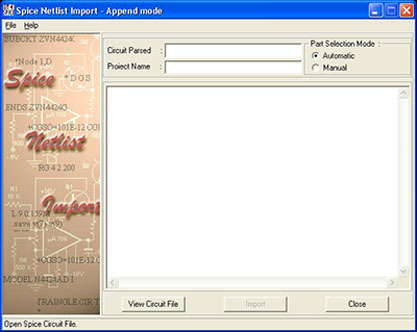

Spice Netlist Import allows to import both circuit (*.cir) and subcircuit (*.sbc) files to the system. The schematic diagram is generated by converting the imported file data to the project. All the instance parameters and model parameters are set during conversion. The circuit and parameters are set for various analyses as specified in the circuit file.

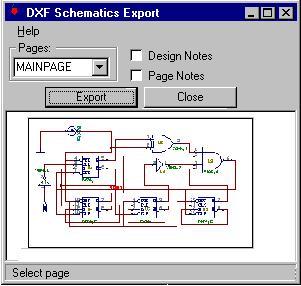

Schematic DXF Export is an application that allows to export the EDWinXP schematic graphics to AutoCAD DXF format.

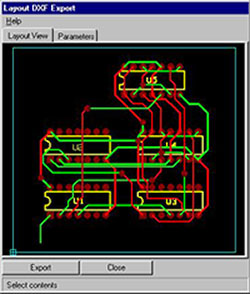

Layout DXF Export is an application that allows to export the EDWinXP layout graphics to AutoCAD DXF format