Binary Gray Converter

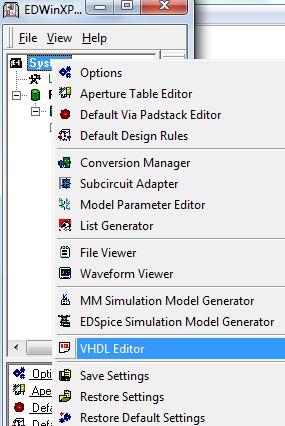

- Right Click on System from Project Explorer and select VHDL Editor from the List

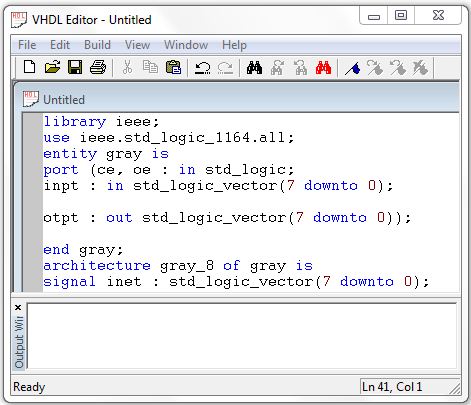

- Enter the following code in the workspace provided in the VHDL Editor window

entity gray is

port (ce, oe : in std_logic;

inpt : in std_logic_vector(7 downto 0);

otpt : out std_logic_vector(7 downto 0));

end gray;

architecture gray_8 of gray is

signal inet : std_logic_vector(7 downto 0);

begin

process (ce, inpt)

begin

if ce = '1' then

inet(7) <= inpt(7);

for i in 0 to 6 loop

inet(i) <= inpt(i+1) xor inpt(i);

end loop;

end if;

process (oe)

begin

if oe = '1' then

for i in 0 to 7 loop

otpt(i) <= inet(i);

end loop;

else

otpt <= "ZZZZZZZZ";

end if;

end process;

end gray_8;

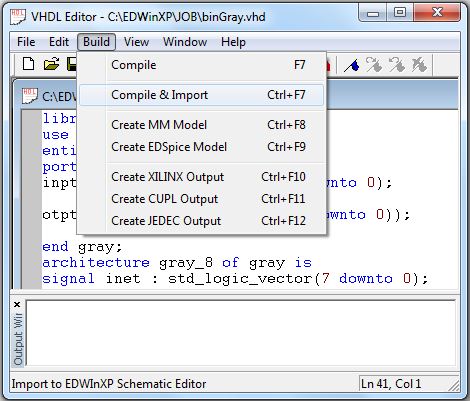

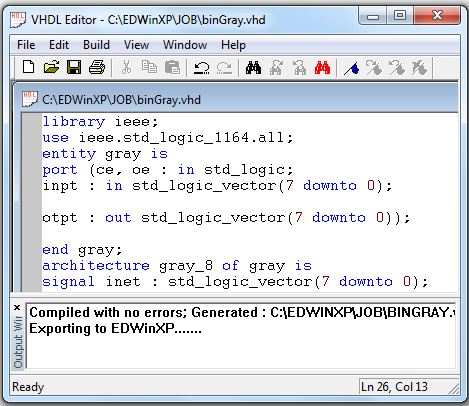

- Save the file (.vhd) and compile the code using Compile & Import option from Build menu.It compiles the source file and generates wirelist (*.wrs) output file

- Output window shows the status of errors

- Click on Import button in Netlist/Wirelist Export&Import window.

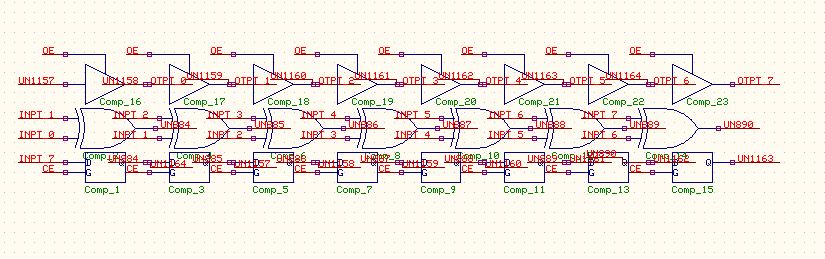

- Open Schematic Editor,Autoplace the components by selecting Tools|Autoplace.

- Autoconnect the components by selecting menu Tools|Connections.Select option tool Autconnect all wires from Connect components

- Pcb layout creation is not possible for a schematic using vhdl as its component part includes only symbol hence couldn't pack components.